# Development of an FPGA-Based SPWM Generator for High Switching Frequency DC/AC Inverters

Matina Lakka, Eftichios Koutroulis, Member, IEEE, and Apostolos Dollas, Senior Member, IEEE

Abstract—The digital implementations of Sinusoidal Pulse Width Modulation (SPWM) generators have dominated over their counterparts based on analog circuits. In this paper, an FPGAbased SPWM generator is presented, which is capable to operate at switching frequencies up to 1 MHz (requiring FPGA operation at 100-160 MHz), thus it is capable to support the high switching frequency requirements of modern single-phase dc/ac power converters. The proposed design occupies a small fraction of a medium-sized FPGA and, thus, can be incorporated in larger designs. Additionally, it has a flexible architecture that can be tuned to a variety of single-phase dc/ac inverter applications. The postlayout simulation and experimental results confirm that compared to the past-proposed SPWM generation designs, the SPWM generator presented in this paper exhibits much faster switching frequency, lower power consumption, and higher accuracy of generating the desired SPWM waveform.

Index Terms—DC/AC inverter, field programmable gate array (FPGA), high frequency, sinusoidal pulse width modulation (SPWM).

#### I. INTRODUCTION

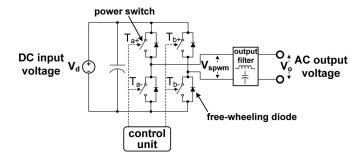

HE dc/ac converters (inverters) are the major power electronic conversion units in renewable energy production, motor drive, and uninterruptible power supply applications [1]–[4]. A simplified block diagram of a single-phase, full-bridge dc/ac power converter (inverter) is depicted in Fig. 1.

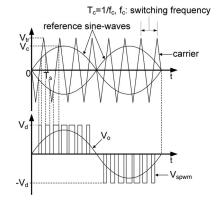

The Sinusoidal Pulse Width Modulation (SPWM) technique is widely employed in order to adjust the dc/ac inverter output voltage amplitude and frequency to the desired value. In this case, the power converter switches (e.g., MOSFETs, IGBTs, etc.) are set to the ON or OFF state according to the result of the comparison between a high-frequency, constant-amplitude triangular wave (carrier) with two low-frequency (e.g., 50 Hz) reference sine waves of adjustable amplitude and/or frequency [5], [6]. In the unipolar SPWM technique illustrated in Fig. 2, the generated pulses are either positive or negative during each halfperiod of the SPWM wave. The high-frequency harmonics of the generated SPWM signal,  $V_{\rm spwm}$  in Fig. 2, are then filtered using

Manuscript received July 19, 2012; revised October 15, 2012 and December 11, 2012; accepted March 12, 2013. Date of current version July 18, 2013. This paper was presented at the 2011 International Conference on Field Programmable Logic and Applications (FPL), pp. 15–19, September 2011. Recommended for publication by Associate Editor K.-B. Lee

The authors are with the Department of Electronic and Computer Engineering, Technical University of Crete, Chania, GR-73100, Greece (e-mail: matinalakka@gmail.com; efkout@electronics.tuc.gr; dollas@ece.tuc.gr).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2013.2253216

Fig. 1. Block diagram of a single-phase, full-bridge dc/ac power converter.

Fig. 2. Unipolar SPWM technique.

a low-pass LC-, LCL- or LLCL type filter [5], [7], thus producing the high-power and low-frequency sinusoidal waveform  $V_o$  at the output terminals of the dc/ac inverter. The amplitude of  $V_o$  (V) is calculated as follows:

$$\widehat{V_o} = M \cdot V_d = \frac{\widehat{V_c}}{\widehat{V_{\rm tr}}} \cdot V_d \tag{1}$$

where  $V_d\left(V\right)$  is the dc input voltage of the dc/ac inverter,  $\widehat{V_c}$ ,  $\widehat{V_{\mathrm{tr}}}$  (V) are the amplitudes of the reference sine and carrier signals, respectively, and M is the modulation index.

Increasing the switching frequency of the triangular wave  $f_c$  results in a reduction of the dc/ac inverter output filter size and cost [8]. Depending on their nominal power rating, the dc/ac inverters typically operate at switching frequencies in the range of 1–100 kHz [9], [10]. A dc/ac inverter comprised of four cascaded Z-source inverter modules, which have been built using Gallium Nitride devices operating at a 1-MHz switching frequency, is proposed in [11]. This trend of increasing the operating switching frequency is expected to continue in the near future [12], [13] due to the recent development of Silicon Carbide power semiconductors, such as JFETs, MOSFETs,

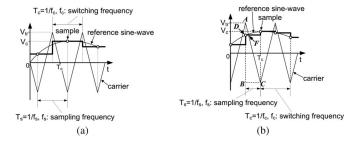

Fig. 3. Reference sine-wave digital representation in past-proposed SPWM generator design methods: (a) sampling at the nadirs and (b) sampling at both the nadirs and the peaks of the carrier wave.

and Schottky diodes [14]–[18], which are capable to operate at switching frequencies up to 3 MHz with low-power losses [19]. Thus, in case that this semiconductor technology is applied then a tenfold increase of the switching frequency is predicted in [20], compared with that of the conventional dc/ac inverters.

The digital SPWM generator implementations have dominated over their counterparts based on analog circuits, since they offer higher noise immunity and less susceptibility to voltage and temperature variations [21]. Typically, microcontrollers, Digital Signal Processors (DSPs) or Field Programmable Gate Arrays (FPGAs) are used for the implementation of the SPWM generation unit and the execution of dc/ac inverter control algorithms (e.g., output voltage regulation, fuzzy logic, motor speed control, etc.) [22]. The integration of both the control and SPWM subsystems in the same chip has the advantage of reducing the design complexity and the total system cost [23], [24]. However, the microcontroller- [25] and DSP-based [26], [27] implementations of the SPWM generator units developed so far operate at low switching frequency levels (i.e., 1–10 kHz). As discussed in [28], the computational speed of microprocessors and DSPs imposes an upper limit on the maximum switching frequency that can be generated using software-based SPWM generation techniques.

Using FPGAs for the development of the dc/ac inverter control logic has widely emerged during the last years since they are considered as a powerful and cost-effective solution [29]. Compared to the microcontroller and DSP-integrated circuits, FPGAs have the advantage of flexibility in case of changes and they enable the reduction of the execution time of the dc/ac inverter control algorithm due to their capability to integrate digital hardware with high speed and parallel processing features [30]–[35].

In the FPGA-based SPWM generation units presented in [21], [24], [36]–[41], the triangular wave is implemented in the form of an up-down counter. Depending on the implementation, the reference sine wave is sampled with a sampling frequency equal to  $f_s$  (regular-sampled pulse width modulation (PWM)) at the time instants corresponding either only to the nadirs [see Fig. 3(a)], or only to the peaks (symmetric modulation), or both at the nadirs and the peaks of the carrier wave [asymmetric modulation, Fig. 3(b)]. The corresponding samples are stored in digital format in a lookup table (LUT) implemented in the FPGA internal memory. The SPWM control signals are produced by comparing the corresponding values of the sinusoidal and car-

rier digital signals. Using these techniques, SPWM switching frequencies in the range of 1.157–20 kHz have been achieved. The same design method has been applied in [23] for the development of an SPWM signal generation SoC based on the OpenRISC1200 32-bit RISC processor core.

Targeting at the reduction of the SPWM generator memory requirements, the sinusoidal wave is produced in [42] using an FPGA-based implementation of the Coordinate Rotation Digital Computer (CORDIC) algorithm. A 5-kHz switching frequency has been achieved in this case. Although this implementation does not require the use of a hardware multiplier, it is characterized by a slower speed compared to the LUT-based SPWM units. The CORDIC algorithm has also been applied in [43] for the development of an integrated circuit performing the generation of a 5-kHz SPWM wave using 0.18-μm CMOS technology.

In [44], an LUT is used to store the reference sine-wave digital values corresponding to the time instants of the peaks and nadirs of the triangular wave. The width of each pulse is calculated using an equation based on the similarity of the triangles ABC and ADF depicted in Fig. 3(b). This design method has been validated in case of a 1-kHz switching frequency. A similar approach is also proposed in [45].

In [46], the SPWM pulse train is produced by comparing the sinusoidal and triangular signals generated according to the direct digital synthesis (DDS) technique. The comparison is performed using a high-speed analog comparator. The DDS approach is also used in [47] for the development of a digital SPWM generator chip using 0.35- $\mu$ m CMOS technology. The maximum clock frequency of this chip is 50 MHz. In [48], the SPWM unit is composed of a DSP chip accomplishing the calculation of the widths of the individual pulses comprising the SPWM wave, which communicates through a parallel port with an FPGA-based unit producing the SPWM control signals.

The regular-sampled PWM technique presented in [28], [49], targets to reduce the amount of computation time required in order to facilitate the generation of higher switching frequencies online and in real time. In this technique, the pulse width is calculated once and used over N consecutive switching edges of the SPWM wave pulses. Then, a new sample of the reference sine wave is acquired. Thus, the sampling frequency  $f_s$  is reduced by an integer factor of N, resulting in the following relationship with the corresponding carrier frequency  $f_c$ :

$$f_s = f_c/N. (2)$$

Consequently, the number of calculations required to produce the complete SPWM waveform is N times less than in the conventional SPWM generation methods.

A common disadvantage of the previously proposed SPWM generators described previously is that they have been designed to operate at low-switching frequencies,  $f_c$  (i.e., 1–20 kHz), while their operation at higher switching frequencies has not been explored yet. In this paper, an FPGA-based SPWM generator is presented, which is capable to operate at switching frequencies up to 1 MHz; thus, it is capable to support the high switching frequency requirements of modern single-phase dc/ac power converters. Compared to the past-proposed SPWM generators, in the proposed architecture the values of both the

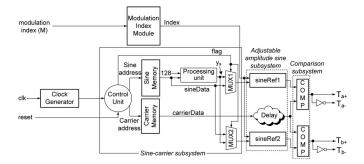

Fig. 4. Architecture of the proposed SPWM generation unit.

reference sine and triangular waves are stored in the FPGA device Block RAMs (BRAMs) in order to exploit their one-clock-cycle access time, thus providing a much higher switching-frequency capability. The proposed design exhibits architectural flexibility features, enabling the change of the SPWM switching frequency and modulation index either internally, or externally. The proposed SPWM unit has been implemented in a single chip in order to enable the reduction of the complexity, cost, and development time of the dc/ac inverter control unit.

The architecture of the proposed FPGA-based SPWM generator is analyzed in Section II, and the simulation and experimental results are presented in Section III. Finally, the performance of the FPGA generator presented in this paper is compared to that of the past-proposed systems, and the corresponding results are analyzed in Section IV.

# II. PROPOSED SPWM GENERATOR

The architecture of the proposed SPWM generation unit is presented in Fig. 4. The system inputs are the modulation index of the output SPWM wave M in single precision floating point arithmetic ranging from 0 to 1, as well as the "clock" and "reset" signals.

The architecture of the proposed system has been built using 8-bit fixed-point arithmetic and it consists of five subsystems, which implement the SPWM generation algorithm. The values of a sinusoidal wave, mathematically being in the range [-1, 1], have been adapted in the proposed architecture to the equivalent range of [0, 255] with the zero point corresponding to the discrete value of "128."

#### A. Clock Generator Subsystem

The "Clock generator" subsystem takes as input the FPGA input clock and produces a new clock signal used by the digital circuits of the proposed SPWM generator, such that the desired SPWM switching frequency  $f_c$  specified by the designer/user is generated. A two-state finite state machine (FSM) is initially used to set the input clock frequency  $f_{\rm clk}$  to  $f_{\rm clk}/2$  and then a Digital Clock Manager module adapts this frequency to the desired value. The Very high speed integrated circuit Hardware Description Language (VHDL) code of the DCM module is illustrated in Fig. 5. The FSM is kept constant for every different switching frequency, while only the operational parameters "CLKFX MULTIPLY" and "CLKFX DIVIDE" of the DCM

Fig. 5. VHDL code of the DCM module in the "Clock generator" subsystem.

module are changed according to the switching frequency requirements of the SPWM output waveform. Thus, the proposed SPWM generator is flexible to be adapted to the generation of any operating switching frequency specified by the system designer/user.

## B. Modulation Index Subsystem

The "Modulation index" subsystem is used to convert the floating-point modulation index M, which is input in the proposed SPWM generation system  $(M \in [0, 1])$  to the corresponding value in fixed-point arithmetic.

Initially, the value of M is transformed into a new floating point value  $y_M$  according to the following equation:

$$y_M = M \cdot (2^{n-1} - 1) + 2^{n-1} \tag{3}$$

where n is the digital word length of the architecture.

Increasing the value of n enables to control the modulation index of the generated SPWM wave with higher resolution, but also results in higher requirements for FPGA device resources. The floating point value produced is then converted into a fixed-point value ranging from 0 to 255, via a float-to-fixed point conversion unit, thus producing the "Index" output of the "Modulation index" subsystem depicted in Fig. 4.

# C. Sine-Carrier Subsystem

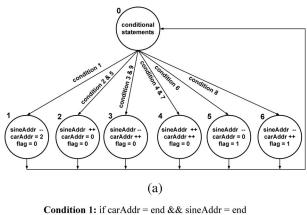

The "Sine-Carrier" subsystem consists of the control unit, two BRAMs, which contain samples of the sinusoidal and triangular (i.e., carrier) waves and two multiplexers that produce the two constant-amplitude reference sine waves used for the production of the SPWM output signals. The BRAMs of the sine wave and carrier operate as LUTs. Both the sinusoidal and triangular waves are sampled and quantized with the same sampling frequency  $f_s$  using MATLAB (e.g.,  $f_s = 4$ , 8 MHz, etc.). In order to minimize the utilization of the FPGA resources, only the values of the first quarter of the constant-amplitude

Condition 1: if carAddr = end && sineAddr = end goto 1 Condition 2: elsif carAddr = end && sineAddr!=

Condition 2: elsif carAddr = end && sineAddr != end goto 2

Condition 3: elsif carAddr!= end && sineAddr = end goto 3

Condition 4: elsif carAddr != end && sineAddr != end goto 4

Condition 5: elsif carAddr = end && sineAddr = start goto 2

**Condition 6:** elsif carAddr = end && sineAddr = 1 goto 5

Condition 7: elsif carAddr != end && sineAddr = start goto 4

**Condition 8:** elsif carAddr = !end && sineAddr = 1

Condition 9: else goto 3

(b)

Fig. 6. FSM of the control unit in the proposed SPWM generator: (a) flowchart and (b) pseudocode of the conditional statements.

sine-wave period (i.e., during the time interval  $0 - \pi/2$ ) are stored in the corresponding BRAM, while the values of the sine wave during the time interval  $\pi/2 - 2\pi$  are calculated by mirroring and inverting the values of the first quarter. The BRAM of the carrier contains the values of a complete period of the reference triangular wave. Consecutive addresses of both memories ("Sine address" and "Carrier address," respectively, in Fig. 4) are generated in every clock cycle by the control unit. The control unit also produces a "flag" signal, which is responsible for the retrieval of the sine-wave values during the time interval  $\pi - 2\pi$  of the reference sine-wave period. The BRAM of the constant-amplitude sinusoidal wave is scanned up and down four times, since this memory contains only the values during the first quarter of the sinusoidal-wave period, as analyzed previously. The FSM generating the addresses of the sinusoidal and carrier memory pointers, "sineAddr" and "carAddr," respectively, is depicted in Fig. 6(a). The first state of this FSM (i.e., "State 0") contains all possible conditions of the memory address pointers, which are listed in the pseudocode illustrated in Fig. 6(b). The value of the "flag" signal determines the up or down direction of consecutive accesses performed for retrieving the data stored in the BRAM memory of the reference sine wave. While "flag" is set to 0, the multiplexer "MUX1" outputs the data read from the constant-amplitude sinusoidal memory

("sineData" in Fig. 4). Otherwise, "MUX1" outputs the values corresponding to the second half-cycle (i.e., during  $\pi-2\pi$ ) of the constant-amplitude sinusoidal wave (parameter " $y_s$ " in Fig. 4).

These values are produced by the processing unit of the "Sinecarrier subsystem" by converting the positive values stored in the sinusoidal memory to the corresponding negative values, according to the following equation:

$$y_s = x - [(x - 2^{n-1}) \times 2] \tag{4}$$

where x is the positive value stored in the BRAM of the sine wave.

The multiplexer "MUX2" in Fig. 4 is used for the production of the second constant-amplitude reference sine wave, which operates with a 180° phase difference compared with the one analyzed above.

#### D. Adjustable Amplitude Sine Subsystem

The "Adjustable amplitude sine" subsystem takes as input the constant-amplitude reference sinusoidal values produced by the "Sine-Carrier" subsystem and generates a sinusoidal digital signal  $y_a$  with an amplitude adjustable according to the value of the modulation index M which is an input in the proposed SPWM generation system. The value of  $y_a$  is in the range 0–255 and it is calculated as follows:

$$y_a = \frac{(y - 2^{n-1}) \times (\text{Index} - 2^{n-1})}{(2^{n-1} - 1)} + 2^{n-1}$$

(5)

where y is the value of the constant-amplitude reference sine wave and *Index* is the output of the "Modulation Index" subsystem, described in Section II-B.

#### E. Comparison Subsystem

The "Comparison" subsystem implements the comparison between the high-frequency constant-amplitude triangular wave (carrier) with the two low-frequency reference sine waves, using two comparators ("COMP" in Fig. 4). The control signals  $T_{a+}$ ,  $T_{a-}$ ,  $T_{b+}$ , and  $T_{b-}$  of the single-phase dc/ac inverter power switches depicted in Fig. 1 are generated from the outputs of the corresponding comparators of this subsystem, thus forming the SPWM wave ( $V_{\rm spwm}$  in Figs. 1 and 2) at the dc/ac inverter output terminals. The outputs of the comparators in the "Comparison" subsystem (i.e., control signals  $T_{a+}$  and  $T_{b+}$ ) are equal to one when the corresponding output of the "Adjustable amplitude sine" subsystem described in Section II-C is equal to or greater than the current digital value of the carrier signal. The DC/AC inverter control signals  $T_{a-}$  and  $T_{b-}$  are produced by inverting  $T_{a+}$  and  $T_{b+}$ , respectively.

#### III. VALIDATION AND PERFORMANCE EVALUATION

The performance of the proposed FPGA-based SPWM generator has been evaluated on an actual design, which has been fully implemented and downloaded to an FPGA board. The digital word length of the implemented architecture has been set equal to n = 8, while the frequency of the reference sine waves

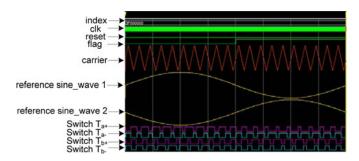

Fig. 7. Major internal signals of the proposed system and the SPWM outputs generated in case that  $f_c=1\,\mathrm{kHz}, f_s=4\,\mathrm{MHz},$  and M=0.5.

is 50 Hz. Several simulation and experimental tests were performed in order to verify the correct operation of the proposed SPWM generator and quantify its ability to accurately produce the desired SPWM waveforms. As analyzed next, the results of this evaluation process are universal, independently from the type of the target single-phase dc/ac inverter application, where the proposed system will be incorporated. The simulation and experimental results presented in this section demonstrate the ability of the proposed SPWM generator to operate over a wide range of switching frequencies (1 kHz–1 MHz) and modulation index values (0–1) in single-phase dc/ac inverter applications.

#### A. System Validation by Simulation

The architecture presented in the previous section has been synthesized using the VHDL language and its correct operation has been verified at both low- and high-carrier frequency levels using the ModelSim 6.3f simulator. The major internal signals of the proposed system and the SPWM outputs in case that  $f_c=1~\mathrm{kHz}, f_s=4~\mathrm{MHz},$  and  $M=0.5~\mathrm{are}$  plotted in Fig. 7. A low-carrier frequency has been used in this example only for demonstration purposes, since it enables the easy discrimination of all SPWM pulses produced within a period of the reference sine wave and the observation of their width.

As analyzed in Section II, the SPWM output is generated at the intersection of the sinusoidal and triangular waveforms at certain sampling instants. When the value of each sine wave is higher than the triangular wave value, the output pulse is set to logical "1," else it is set to logical "0."

#### B. Experimental Results

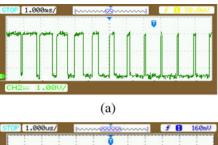

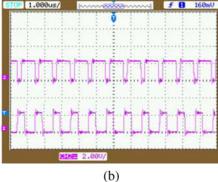

A laboratory prototype of the proposed FPGA-based SPWM generation system (see Fig. 4) was implemented using the commercially available XILINX XUPV5-LX110T development board for downloading the implemented SPWM design, which contains the XC5VLX110T Virtex-5FPGA device. The proposed SPWM generator is suitable for incorporation in single-phase dc/ac inverter applications and as an example, the experimental, oscilloscope measurements of the  $T_{a+}$  SPWM control signal ( $T_{a-}$ ,  $T_{b+}$ , and  $T_{b-}$  exhibit similar patterns) in case that  $f_c=1$  kHz and  $f_c=1$  MHz, respectively, are illustrated in Fig. 8. Using a 1-MHz carrier frequency, results in 20 000 pulses spread over the 1/50 Hz time period of the  $T_{a+}$  signal. Thus, in order to enable the visibility of the individual SPWM pulses,

Fig. 8. Oscilloscope measurements of the  $T_{a+}$  SPWM control signal: (a)  $f_c=1~{\rm kHz},\,f_s=4~{\rm MHz},\,$  and  $M=0.9~{\rm and}\,$  (b)  $f_c=1~{\rm MHz},\,f_s=32~{\rm MHz},\,$  and M=0.5.

two different portions of this signal are illustrated separately in the upper and lower waveforms, respectively, which are plotted in Fig. 8(b).

Then, a unity-gain differential amplifier was used in order to subtract the  $T_{a+}$  and  $T_{b+}$  control signals generated by the proposed SPWM generation system (see Fig. 4), thus producing a wave equivalent to the output SPWM signal of a single-phase dc/ac inverter,  $V_{\text{spwm}}$  in Figs. 1 and 2. This hardware-emulation process has the advantage of low cost, since building an actual power stage of a single-phase dc/ac inverter (including power switches, drivers, etc.) is avoided. Additionally, it enables to evaluate the performance of the proposed SPWM generator without being affected by nonidealities of an experimental prototype dc/ac power inverter (e.g., dead-time effect, power switch finite turn-on, and turn-off times, etc.), which depend on the exact type of the dc/ac inverter application comprising the proposed SPWM generator and deteriorate the quality of the generated SPWM signal [5]. The minimization of the impact of such effects is performed during the design process of the dc/ac inverter; thus, the investigation of their impact on the quality of the SPWM output voltage of the dc/ac inverter is not within the scope of this paper. The hardware-emulation process described previously has been applied in order to experimentally evaluate the performance of both the new SPWM generator presented in this paper, as well as that of the past-proposed SPWM generation units. The corresponding experimental results are presented in the following paragraphs of this paper.

The Fast Fourier Transforms (FFTs) of the experimentally measured SPWM output waveforms, which are produced by the hardware emulation process described previously, in case that the SPWM switching frequency  $f_c$  is 1 kHz and 1 MHz are illustrated in Fig. 9(a) and (b), respectively. It is observed that, as expected due to the attributes of the unipolar SPWM

Fig. 9. FFT of the experimentally measured unipolar SPWM output waveform for single-phase applications: (a)  $f_c=1\,\mathrm{kHz}, f_s=4\,\mathrm{MHz}$ , and  $M=0.9\,\mathrm{and}$  (b)  $f_c=1\,\mathrm{MHz}, f_s=32\,\mathrm{MHz}$ , and M=0.5.

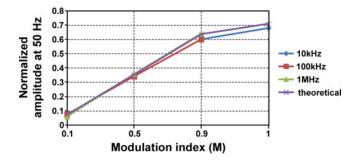

Fig. 10. Normalized experimental and theoretical amplitude at 50 Hz of the generated SPWM waveform using the proposed SPWM generator for  $f_s=4~\mathrm{MHz}, M=0.1-1$ , and  $f_c=10~\mathrm{kHz}-1~\mathrm{MHz}.$

technique, the generated SPWM signal consists of the fundamental at 50 Hz, while the harmonics appear as sidebands at multiples of twice the switching frequency. These experimental results also confirm the correct operation of the proposed SPWM generator at high switching frequency (i.e., up to 1 MHz).

The experimentally measured and theoretically calculated amplitude of the generated SPWM waveform at the fundamental frequency (i.e., 50 Hz), both normalized over the amplitude of the SPWM pulses [i.e.,  $V_d$  in (1) and Fig. 2], for  $f_s=4$  MHz, M=0.1-1, and  $f_c=10$  kHz -1 MHz are displayed in Fig. 10. The deviation  $\Delta V$  (%) between the experimental and theoretical amplitudes of the generated SPWM waveform at the fundamental frequency has been calculated as follows:

$$\Delta V(\%) = \frac{|\text{theoretical} - \text{experimental}|}{\text{theoretical}} \cdot 100\%.$$

(6)

The average value of  $\Delta V$  (%) over the 0.1–1 range of the modulation index, in each switching frequency, is 3.9–6.8%. Thus, it is verified that using the proposed SPWM generator the amplitude of the sinusoidal wave at the output of a single-phase dc/ac inverter can be controlled with high accuracy.

# C. Power Consumption and System Resources

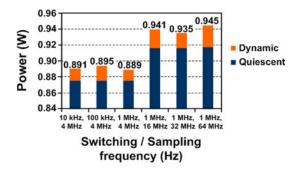

A post place-and-route analysis of the implemented system has been performed using the XILINX ISE Design Suite 10.1 software. The dynamic, quiescent, and total power consumption of the FPGA device in the post place-and-route implementation of the proposed system have been derived using the power analyzer of the XILINX ISE Design Suite 10.1 software and they are plotted in Fig. 11 as a function of  $f_c/f_s$ .

The total power consumption at the 1 / 64 MHz upper end is 6.1% higher compared to that at 10 kHz/4 MHz. Depending

Fig. 11. Power consumption of the proposed SPWM generation system for various values of  $f_c/f_s$ , in case of the XC5VLX110T Virtex-5 XILINX FPGA device.

on the values of  $f_c$  and  $f_s$ , 97.04–98.43% of the total power consumption corresponds to the quiescent power, while the rest is consumed during dynamic operating conditions.

The resources required for the implementation of the full system are presented in Table I for various combinations of the sampling and carrier frequencies  $f_s$  and  $f_c$  respectively. The corresponding maximum operating clock frequency values are shown in the last row of Table I. It is observed that the proposed design is capable to operate at switching frequency values up to 1 MHz, thus covering the requirements of modern high-switching-frequency single-phase dc/ac power converters, as analyzed in Section I.

Also, a low percentage of the FPGA device logic and memory blocks are occupied by the proposed SPWM generation architecture enabling the implementation of additional dc/ac inverter control algorithms in the same FPGA IC (e.g., for regulating the dc/ac inverter output voltage, current or frequency to the desired value, etc.).

Increasing the sampling frequency  $f_s$  results in a more accurate calculation of the widths of the individual SPWM pulses, but, as shown in Table I, the BRAM memory requirements for the implementation of the LUTs described in Section II-C for the sinusoidal and carrier waves are also increased. Additional tests performed for higher sampling frequencies indicated that the BRAMs are the critical resource that restricts further increase of the sampling frequency (e.g., to 128, 256 MHz, etc.).

# IV. PERFORMANCE COMPARISON WITH THE PAST-PROPOSED SPWM GENERATORS

In order to compare their performance with that of the SPWM generation unit, which is presented in this paper, the major past-proposed SPWM generation methods were also implemented and evaluated using simulation and experimental tests and the corresponding results are presented in this section. The systems developed are those based on the past-proposed techniques that implement the triangular wave using an up-down counter, and the sampled reference sinusoidal wave is stored in digital format in an LUT implemented in the FPGA internal memory [28], [38], [41], [49]. The reference sine wave is sampled at the time instants corresponding to either the nadirs, peaks, both at the nadirs and the peaks of the carrier wave or with one sample per N=3 carrier cycles (undersampling), as analyzed

| $f_c / f_s$                | 1kHz /<br>4MHz          | 100kHz /<br>4MHz        | 500kHz /<br>4MHz     | 1MHz /<br>4MHz       | 100kHz /<br>16MHz       | 500kHz /<br>16MHz       | 1MHz /<br>16MHz         | 100kHz /<br>64MHz       | 500kHz /<br>64MHz    | 1MHz /<br>64MHz      |

|----------------------------|-------------------------|-------------------------|----------------------|----------------------|-------------------------|-------------------------|-------------------------|-------------------------|----------------------|----------------------|

| DSPs                       | 6 / 64<br>(9%)          | 6 / 64<br>(9%)          | 6 / 64 (9%)          | 6 / 64 (9%)          | 6 / 64<br>(9%)          | 6 / 64<br>(9%)          | 6 / 64<br>(9%)          | 6 / 64<br>(9%)          | 6 / 64 (9%)          | 6 /64<br>(9%)        |

| Slice<br>Registers         | 3447 /<br>69120<br>(4%) | 3441 /<br>69120<br>(4%) | 3438 /<br>69120 (4%) | 3437 /<br>69120 (4%) | 3445 /<br>69120<br>(4%) | 3442 /<br>69120<br>(4%) | 3441 /<br>69120<br>(4%) | 3454 /<br>69120<br>(4%) | 3451 /<br>69120 (4%) | 3450 /<br>69120 (4%) |

| Slice<br>LUTs              | 2860 /<br>69120<br>(4%) | 2843 /<br>69120<br>(4%) | 2838 /<br>69120 (4%) | 2840 /<br>69120 (4%) | 2852 /<br>69120<br>(4%) | 2846 /<br>69120<br>(4%) | 2846 /<br>69120<br>(4%) | 2901 /<br>69120<br>(4%) | 2893 /<br>69120 (4%) | 2893 /<br>69120 (4%) |

| BRAMs                      | 6 / 148<br>(4%)         | 6 / 148<br>(4%)         | 6 / 148 (4%)         | 6 / 148 (4%)         | 21 / 148<br>(14%)       | 21 / 148<br>(14%)       | 21 / 148<br>(14%)       | 79 / 148<br>(52%)       | 79 / 148<br>(52%)    | 79 / 148<br>(52%)    |

| max.<br>clock<br>frequency | 158MHz                  | 155MHz                  | 144MHz               | 149MHz               | 126MHz                  | 138MHz                  | 131MHz                  | 96MHz                   | 97MHz                | 99MHz                |

${\it TABLE~I}$  FPGA Resources Required by the Proposed SPWM Architecture for Various Values of  $f_c$  and  $f_s$

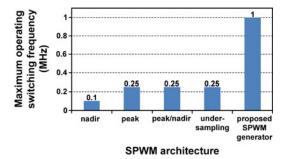

Fig. 12. Experimentally measured maximum operating switching frequency of the SPWM architectures under study.

in Section I. These architectures were adapted such that they produce a unipolar SPWM output for single-phase full-bridge dc/ac inverters, in order to be fully compatible with the new SPWM generator proposed in this paper. Both the newly and the past-proposed SPWM generator architectures were fully implemented on the XC5VLX110T Virtex-5 XILINX FPGA device.

The maximum possible operating switching frequency that can be achieved by each of the SPWM generation architectures has been experimentally measured and it is presented in Fig. 12. It is observed that compared to the past-proposed architectures, the SPWM generation unit proposed in this paper is capable to operate at a much higher maximum switching frequency.

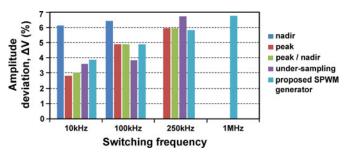

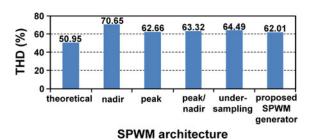

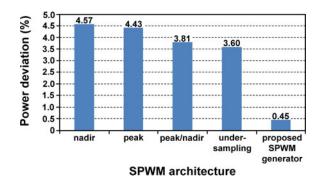

The average deviation  $\Delta V$  (%) for M=0.1-1 between the experimentally measured and the theoretically calculated amplitude of the fundamental frequency (i.e., 50 Hz) in the SPWM waveform generated by each of the SPWM architectures under study at various switching frequencies is depicted in Fig. 13. Except the sampling-at-nadir design, the rest of the architectures obtain similar performance in each switching frequency. However, only the proposed method is capable to operate up to 1 MHz and simultaneously retain the high-accuracy feature of the generated SPWM output signal. The SPWM generation method based on the triangles similarity [44], [45] was also implemented initially, but the resulting average value of  $\Delta V=66\%$  for a 10-kHz switching frequency was considered unacceptably high. Thus, the operation of this SPWM technique at higher switching frequencies was not further investigated.

Fig. 13. Average deviation for M=0.1-1 between the experimental and theoretical amplitude at 50 Hz in the SPWM waveform generated by each of the SPWM architectures under study at various switching frequencies.

Fig. 14. Experimentally measured THD of the SPWM waveform produced by each architecture under study and the THD of the corresponding theoretical SPWM waveform, in case that  $f_c=1\,\mathrm{kHz}$  and M=0.9.

An additional metric used to investigate the quality of the generated SPWM waveform is the Total Harmonic Distortion (THD) that is defined as follows [5]:

THD (%) =

$$\frac{\sqrt{\sum_{h \neq 1} V_h^2}}{V_1} \cdot 100 \%$$

(7)

where  $V_1$  (V) is the RMS value of the fundamental (e.g., 50 Hz) and  $V_h$  (V) is the RMS value of the hth harmonic of the SPWM signal.

The experimentally measured THD (%) of the SPWM waveform produced by each architecture under study for  $f_c=1~\rm kHz$  and M=0.9 and the THD of the corresponding theoretical SPWM waveform, which is used as a reference, are presented in Fig. 14. A low switching frequency has been applied in order to adapt to the low-input-signal bandwidth specifications of the laboratory instrument used to perform these measurements (HAMEG HM8027 distortion meter). It is observed that the

Fig. 15. Total power consumption of the SPWM generator architectures at their maximum operating switching frequency.

Fig. 16. Average deviation of the power consumption when operating at switching frequencies lower than the maximum possible switching frequency of each SPWM generation architecture.

THD (%) of the SPWM signal produced by the proposed SPWM generator deviates from the THD of the corresponding theoretical SPWM waveform by 11.06%, while the past-proposed architectures deviate by 11.71–19.69%. Thus, the SPWM waveform produced using the proposed system achieves a more accurate representation of the desired SPWM wave.

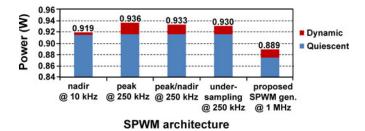

The dynamic, quiescent, and total power consumption of the FPGA device for each of the post place-and-route implementations of all SPWM generator architectures under study, when operating at their maximum possible switching frequency, have been derived using the power analyzer of the XILINX ISE Design Suite 10.1 software and they are displayed in Fig. 15. The total power consumption of the proposed architecture, although it operates at its 1-MHz maximum switching frequency, is less than that of the past-proposed SPWM generation systems by 3.26–5.02%.

In order to investigate the variability of the power consumed by each of the SPWM generation architectures when operating at switching frequencies lower than the maximum possible operating switching frequency, the corresponding average deviations are illustrated in Fig. 16. The proposed architecture exhibits the highest stability in terms of this power consumption, thus indicating its suitability for incorporation in a wide range of single-phase dc/ac inverter applications with different switching frequency requirements.

In terms of the FPGA resources required, all SPWM generator architectures occupy a small fraction ( $\approx$ 9%) of the medium-sized FPGA device used. The BRAMs are the critical resource that restricts further increase of the sampling frequency of the SPWM generator proposed in this paper. The next critical re-

sources are the DSPs that occupy 3% more space in the FPGA device of the proposed SPWM generator.

## V. CONCLUSION

The SPWM principle is widely used in dc/ac inverters in energy conversion and motor drive applications. The past-proposed SPWM generators have been designed to operate at low switching frequencies (i.e., 1–20 kHz), while their operation at higher switching frequencies had not been explored so far.

In this paper, an FPGA-based SPWM generator has been presented, which is capable to operate at switching frequencies up to 1 MHz, thus it is able to support the high switching frequency requirements of modern single-phase dc/ac inverters. The proposed design occupies a small fraction of a medium-sized FPGA and, thus, can be incorporated in larger designs, while it has a flexible architecture can be adapted to a variety of single-phase dc/ac inverter applications. Both post place and route simulation results and experimental verification results on actual hardware were presented, demonstrating the successful operation of the proposed SPWM generator at high switching frequencies.

The past-proposed SPWM generation techniques were also implemented and their performance was compared to that of the new architecture presented in this paper. The postlayout simulation and experimental results confirm that the proposed SPWM generator exhibits much faster switching frequency, lower power consumption, and higher accuracy of generating the desired SPWM waveform.

#### REFERENCES

- R. Teodorescu, M. Liserre, and P. Rodríguez, Grid Converters for Photovoltaic and Wind Power Systems, 1st ed. New York, NY, USA: Wiley, 2011.

- [2] N. D. Patel and U. K. Madawala, "A bit-stream-based PWM technique for sine-wave generation," *IEEE Trans. Ind. Electron.*, vol. 56, no. 7, pp. 2530–2539, Jul. 2009.

- [3] S. Dasgupta, S. K. Sahoo, and S. K. Panda, "Single-phase inverter control techniques for interfacing renewable energy sources with microgrid - part I: Parallel-connected inverter topology with active and reactive power flow control along with grid current shaping," *IEEE Trans. Power Electron.*, vol. 26, no. 3, pp. 717–731, Mar. 2011.

- [4] S. A. Saleh and M. A. Rahman, "Experimental performances of the single-phase wavelet-modulated inverter," *IEEE Trans. Power Electron.*, vol. 26, no. 9, pp. 2650–2661, Sep. 2011.

- [5] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics: Converters, Applications, and Design*, 3rd ed. New York, NY, USA: Wiley, 2002.

- [6] A. M. Hava and N. O. Çetin, "A generalized scalar PWM approach with easy implementation features for three-phase, three-wire voltage-source inverters," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1385–1395, May 2011.

- [7] W. Wu, Y. He, and F. Blaabjerg, "An LLCL power filter for single-phase grid-tied inverter," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 782–789, Feb. 2012.

- [8] X. Li and A. K. S. Bhat, "A utility-interfaced phase-modulated high-frequency isolated dual LCL DC/AC converter," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 1008–1019, Feb. 2012.

- [9] D. Floricau, G. Gateau, A. Leredde, and R. Teodorescu, "The efficiency of three-level active NPC converter for different PWM strategies," in *Proc.* 13th Eur. Conf. Power Electron. Appl., 2009, pp. 1–9.

- [10] Y. Hayashi, K. Takao, T. Shimizu, and H. Ohashi, "High power density design methodology," in *Proc. Power Convers. Conf.*, 2007, pp. 569–574.

- [11] L. Liu, H. Li, Y. Zhao, X. He, and Z. J. Shen, "1 MHz cascaded Z-source inverters for scalable grid-interactive photovoltaic (PV) applications using GaN device," in *Proc. IEEE Energy Convers. Cong. Expo.*, Sep. 2011, pp. 2738–2745.

- [12] R. Lai, F. Wang, P. Ning, D. Zhang, D. Jiang, R. Burgos, D. Boroyevich, K. J. Karimi, and V. D. Immanuel, "A high-power-density converter," *IEEE Ind. Electron. Mag.*, vol. 4, no. 4, pp. 4–12, Dec. 2010.

- [14] D. Jiang, R. Burgos, F. Wang, and D. Boroyevich, "Temperature-dependent characteristics of SiC devices: Performance evaluation and loss calculation," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 1013–1024, Feb. 2012.

- [15] B. Wrzecionko, D. Bortis, J. Biela, and J. W. Kolar, "Novel AC-coupled gate driver for ultrafast switching of normally off SiC JFETs," *IEEE Trans. Power Electron.*, vol. 27, no. 7, pp. 3452–3463, Jul. 2012.

- [16] J. Valle-Mayorga, C. P. Gutshall, K. M. Phan, I. Escorcia-Carranza, H. A. Mantooth, B. Reese, M. Schupbach, and A. Lostetter, "Hightemperature silicon-on-insulator gate driver for SiC-FET power modules," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4417–4424, Nov. 2012.

- [17] I. Josifovic, J. Popovic-Gerber, and J. A. Ferreira, "Improving SiC JFET switching behavior under influence of circuit parasitics," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3843–3854, Aug. 2012.

- [18] F. Xu, T. J. Han, D. Jiang, L. M. Tolbert, F. Wang, J. Nagashima, S. J. Kim, S. Kulkarni, and F. Barlow, "Development of a SiC JFET-based six-pack power module for a fully integrated inverter," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1464–1478, Mar. 2013.

- [19] K. Sheng, Y. Zhang, L. Yu, M. Su, and J. H. Zhao, "High-frequency switching of SiC high-voltage LJFET," *IEEE Trans. Power Electron.*, vol. 24, no. 1, pp. 271–277, Jan. 2009.

- [20] M. Ogawa, S. Ogasawara, and M. Takemoto, "A feedback-type dead-time compensation method for high-frequency PWM inverter Delay and pulse width characteristics," in *Proc. IEEE 27th Annu. Appl. Power Electron. Conf. Expo.*, Feb. 2012, pp. 100–105.

- [21] L. Lei, W. Tian-yu, and X. Wen-guo, "Application of sinusoidal pulse width modulation algorithm in the grid-connected photovoltaic system," in *Proc. Int. Conf. Inf. Technol., Comput. Eng. Manage. Sci.*, 2011, vol. 2, pp. 254–257.

- [22] M. Suetake, I. N. da Silva, and A. Goedtel, "Embedded DSP-based compact fuzzy system and its application for induction-motor V/f speed control," *IEEE Trans. Ind. Electron.*, vol. 58, no. 3, pp. 750–760, Mar. 2011.

- [23] Y. Yang, Y. Wang, and Y. Gao, "Design of digital three-phase SPWM signal generation system based on SoC," in Proc. 9th Int. Conf. Solid-State Integr.-Circuit Technol., 2008, pp. 1889–1892.

- [24] R. K. Pongiannan, S. Paramasivam, and N. Yadaiah, "Dynamically reconfigurable PWM controller for three-phase voltage-source inverters," *IEEE Trans. Power Electron.*, vol. 26, no. 6, pp. 1790–1799, Jun. 2011.

- [25] A. Maiti, S. Choudhuri, J. Bera, T. Banerjee, and S. Maitra, "Development of microcontroller based single phase SPWM inverter with remote control facility," in *Proc. Joint Int. Conf. Power Electron., Drives Energy Syst./Power India*, 2010, pp. 1–5.

- [26] M. F. N. Tajuddin, N. H. Ghazali, I. Daut, and B. Ismail, "Implementation of DSP based SPWM for single phase inverter," in *Proc. Int. Symp. Power Electron. Electr. Drives Autom. Motion*, 2010, pp. 1129–1134.

- [27] W. Song, Z. Xiaoli, Y. Dongxuan, L. Xiaoqin, and H. Aihong, "Design of photovoltaic inverter system based on TMS320F28027," in *Proc. Int. Conf. Comput. Appl. Syst. Model.*, 2010, vol. 2, pp. V2.43–V2..47.

- [28] S. R. Bowes and D. Holliday, "Optimal regular-sampled PWM inverter control techniques," *IEEE Trans. Ind. Electron.*, vol. 54, no. 3, pp. 1547– 1559, Jun. 2007.

- [29] M. P. Aguirre, L. Calvino, and M. I. Valla, "Multilevel current source inverter with FPGA control," *IEEE Trans. Ind. Electron.*, vol. 60, no. 1, pp. 3–10, Jan. 2013.

- [30] Y. Wu, M. A. Shafi, A. M. Knight, and R. A. McMahon, "Comparison of the effects of continuous and discontinuous PWM schemes on power losses of voltage-sourced inverters for induction motor drives," *IEEE Trans. Power Electron.*, vol. 26, no. 1, pp. 182–191, Jan. 2011.

- [31] M. W. Naouar, A. Ammar Naassani, E. Monmasson, and I. Slama Belkhodja, "FPGA-based predictive current controller for synchronous machine speed drive," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 2115–2126, Jul. 2008.

- [32] M. G. Batarseh, W. Al-Hoor, L. Huang, C. Iannello, and I. Batarseh, "Window-masked segmented digital clock manager-FPGA-based digital pulsewidth modulator technique," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2649–2660, Nov. 2009.

- [33] M. Hartmann, S. D. Round, H. Ertl, and J. W. Kolar, "Digital current controller for a 1 MHz, 10 kW three-phase VIENNA rectifier," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2496–2508, Nov. 2009.

- [34] E. Ormaetxea, J. Andreu, I. Kortabarria, U. Bidarte, I. Martínez de Alegría, E. Ibarra, and E. Olaguenaga, "Matrix converter protection and computational capabilities based on a system on chip design with an FPGA," *IEEE Trans. Power Electron.*, vol. 26, no. 1, pp. 272–287, Jan. 2011.

- [35] A. Agarwal and V. Agarwal, "FPGA realization of trapezoidal PWM for generalized frequency converter," *IEEE Trans. Ind. Inf.*, vol. 8, no. 3, pp. 501–510, Aug. 2012.

- [36] S. Z. Mohammad Noor, M. K. Hamzah, N. F. Abdul Rahman, A. F. Hapani, and Z. Idris, "XILINX FPGA design for sinusoidal pulse width modulation (SPWM) control of single-phase matrix converter," in Proc. IEEE Symp. Ind. Electron. Appl., Sep. 2011, pp. 714–719.

- [37] S. Z. Mohammad Noor, M. K. Hamzah, and A. Saparon, "Single phase matrix converter for inverter operation controlled using Xilinx FPGA," in *Proc. IEEE 2nd Int. Power Energy Conf.*, Dec. 2008, pp. 764–769.

- [38] M. S. N. Romli, Z. Idris, A. Saparon, and M. K. Hamzah, "An areaefficient sinusoidal pulse width modulation (SPWM) technique for single phase matrix converter (SPMC)," in *Proc. IEEE 3rd Conf. Ind. Electron. Appl.*, Jun. 2008, pp. 1163–1168.

- [39] H. Hussin, A. Saparon, M. Muhamad, and M. D. Risin, "Sinusoidal pulse width modulation (SPWM) design and implementation by focusing on reducing harmonic content," in *Proc. 4th Asia Int. Conf. Math./Anal. Modell. Comput. Simul.*, 2010, pp. 620–623.

- [40] S. R. S. Raihan and N. A. Rahim, "Modeling of FPGA-based pulse-width modulation for parallel three-phase AC/DC converters," in *Proc. Int. Conf. Tech. Postgraduates*, 2009, pp. 1–3.

- [41] R. K. Pongiannan, P. Selvabharathi, and N. Yadaiah, "FPGA based three phase sinusoidal PWM VVVF controller," in *Proc. 1st Int. Conf. Electr. Energy Syst.*, 2011, pp. 34–39.

- [42] M. A. Rongi, A. Saparon, and M. K. Hamzah, "Sinusoidal pulse width modulation using CORDIC algorithm for single phase matrix converter," in *Proc. IEEE 5th Conf. Ind. Electron. Appl.*, Jun. 2010, pp. 1088–1093.

- [43] M. A. Rongi, A. Saparon, and N. H. Marzuki, "A CORDIC-sinusoidal pulse width modulation using silterra 0.18 μm CMOS technology," in Proc. Int. Conf. Electron. Devices, Syst. Appl., 2010, pp. 76–81.

- [44] L. Jian, Y. Xianggen, Z. Zhe, and X. Qing, "A new three-level NPC inverter based on phase individual DC-link circuit and high quality digital SPWM control technology," in *Proc. Int. Conf. Commun., Circuits Syst.*, 2009, pp. 732–736.

- [45] X.-D. Liu and T. Xu, "Switching time point precision comparison and harmonic analysis of SPWM," in *Proc. IEEE 5th Conf. Ind. Electron.* Appl., Jun. 2010, pp. 1152–1156.

- [46] S. Gao, S. Cao, and Y. Zhang, "Sinusoidal pulse width modulation design based DDS," in *Proc. 2nd Int. Workshop Intell. Syst. Appl.*, 2010, pp. 1–4.

- [47] Y. Yuan, G. Yong, and C. Lijie, "Design and test of novel programmable digital three phases SPWM chip," in *Proc. CES/IEEE 5th Int. Power Electron. Motion Control Conf.*, Aug. 2006, vol. 3, pp. 1–3.

- [48] H. Xu and J. Li, "FPGA based multiplex PWM generator for multilevel converters applied wind power generator," in *Proc. Asia-Pacific Power Energy Eng. Conf.*, 2009, pp. 1–4.

- [49] S. R. Bowes and Y. S. Lai, "Investigation into optimising high switching frequency regular sampled PWM control for drives and static power converters," *IEE-Proc. Electric Power Appl.*, vol. 143, no. 4, pp. 281–293, Jul. 1996.

lion, Greece.

Matina Lakka was born in Belgrade, Serbia, in 1985. She received the B.Sc. and M.Sc. degrees from the Technical University of Crete, Chania, Greece, in 2009 and 2012, respectively.

Her research interests are in the areas of reconfigurable computing, hardware implementation of algorithms for bioinformatic applications, the implementation of image processing algorithms on reconfigurable resources and Wireless Sensor Networks. Currently, she is working at the European Network and Information Security Agency (ENISA), Herak-

Eftichios Koutroulis (M'10) was born in Chania, Greece, in 1973. He received the B.Sc. and M.Sc. degrees from the Technical University of Crete, Chania, Greece, in 1996 and 1999, respectively. He received the Ph.D. degree from the Technical University of Crete, in 2002 in the area of power electronics and Renewable Energy Sources (RES).

He is currently an Assistant Professor at the Department of Electronic and Computer Engineering of the Technical University of Crete. His research interests include power electronics (DC/AC inverters,

DC/DC converters), the development of microelectronic energy management systems for RES, and the design of photovoltaic and wind energy conversion systems.

**Apostolos Dollas** (SM'93) received the B.S., M.S., and Ph.D. degrees in computer science from the University of Illinois at Urbana-Champaign, USA, in 1982, 1984, and 1987, respectively.

He is a Professor of Electronic and Computer Engineering at the Technical University of Crete (TUC), Chania, Greece, where he has served one term as Department Chairman. From 1986 to 1994, he was with the Faculty of the Electrical Engineering and of the Computer Science Departments at Duke University. He was the Director of the Microprocessor and Hard-

ware Laboratory at TUC, from 1994 to 2009. He conducts research, teaches, and publishes in the areas of reconfigurable computing, embedded systems, application specific high-performance digital systems and rapid system prototyping. In all of these areas he places emphasis on the development of fully functional prototypes. He is co-inventor in two issued US Patents.

Dr. Dollas is a Senior Member of the IEEE Computer Society. He belongs to the Eta Kappa Nu and Tau Beta Pi and has received the IEEE Computer Society Golden Core Member award, the IEEE Computer Society Meritorious Service Award, and twice the Department of Computer Science Award for Outstanding Teaching at the University of Illinois at Urbana-Champaign (as a Teaching Assistant). He is co-founder of several IEEE-sponsored international conferences, including FCCM, FPT, RSP, SASP, and TAI and serves in the program committee of many international conferences and workshops, including FCCM, FPL (of which he was General co-Chair in 2011), and FPT.